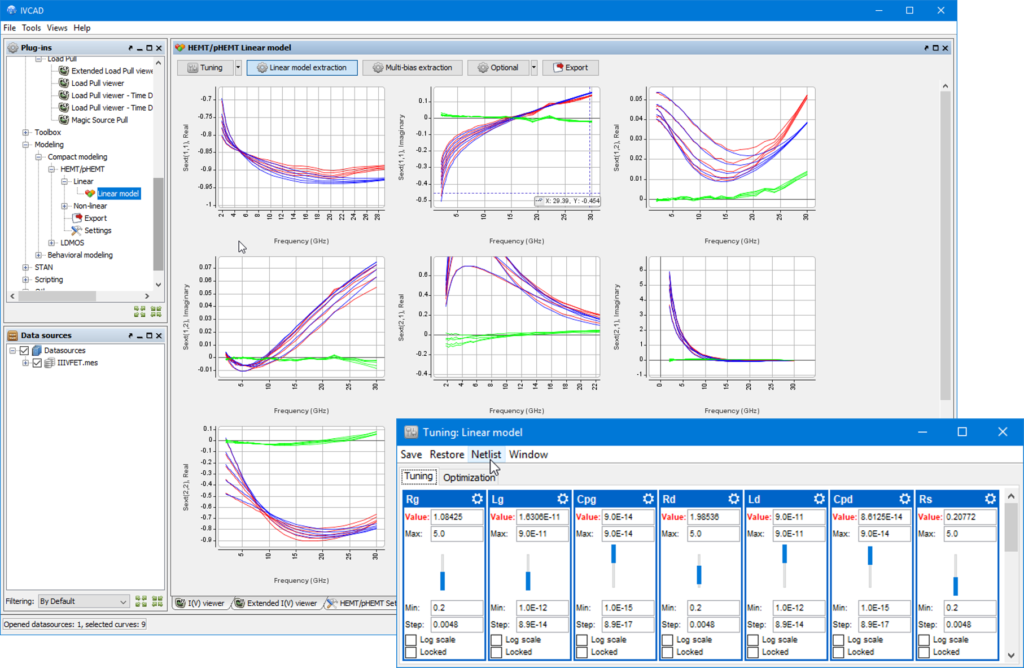

MT930M1 Linear Model Extraction is used easily to determine the extrinsic (parasitic elements) and intrinsic parameters of III-V and LDMOS transistors. Linear modeling fits measured data to linear model equations and can be automatically optimized or manually tuned to solve for values of the extrinsic (Rg, Lg, Cpg, Rd, Ld, Cpd, Rs, Ls) and intrinsic parameters.

Linear model extraction is a critical first step in the transistor modeling process, any errors resulting from linear model inaccuracies will prevent the extraction of nonlinear models. A wizard guides users through a step-by- step process in order to eliminate user errors and ensure first-pass linear model extraction success. Validation is provided by comparing intrinsic elements through a multi-bias extraction. Netlist import and export is available at each level of the linear model extraction process.

AN : Transistor Compact Modeling